Durante la cerimonia di “inaugurazione” per l’avvio della produzione dei chip a 3 nm, tenutasi il 29 dicembre, Liu Deyin, Presidente di TSMC, ha tenuto un discorso nel quale ha fatto il punto della situazione. Attualmente il tasso di rendimento non sarebbe ancora al livello dei chip a 5 nm ma, mentre il colosso continua a lavorare per ottenere risultati migliori, si conferma di molto avanti alla concorrenza: Samsung.

- Qualcomm QCX216 LTE IoT: alte prestazioni e maggiore autonomia

- Ecco il Qualcomm Snapdragon 782G: sostituirà il tanto amato 778G+

- Snapdragon 8 Gen 1 vs Snapdragon 8 Gen 2: schede tecniche a confronto

- Qualcomm presenta le due nuove soluzioni Snapdragon Sound

Snapdragon 8 Gen 3: TSMC e Samsung

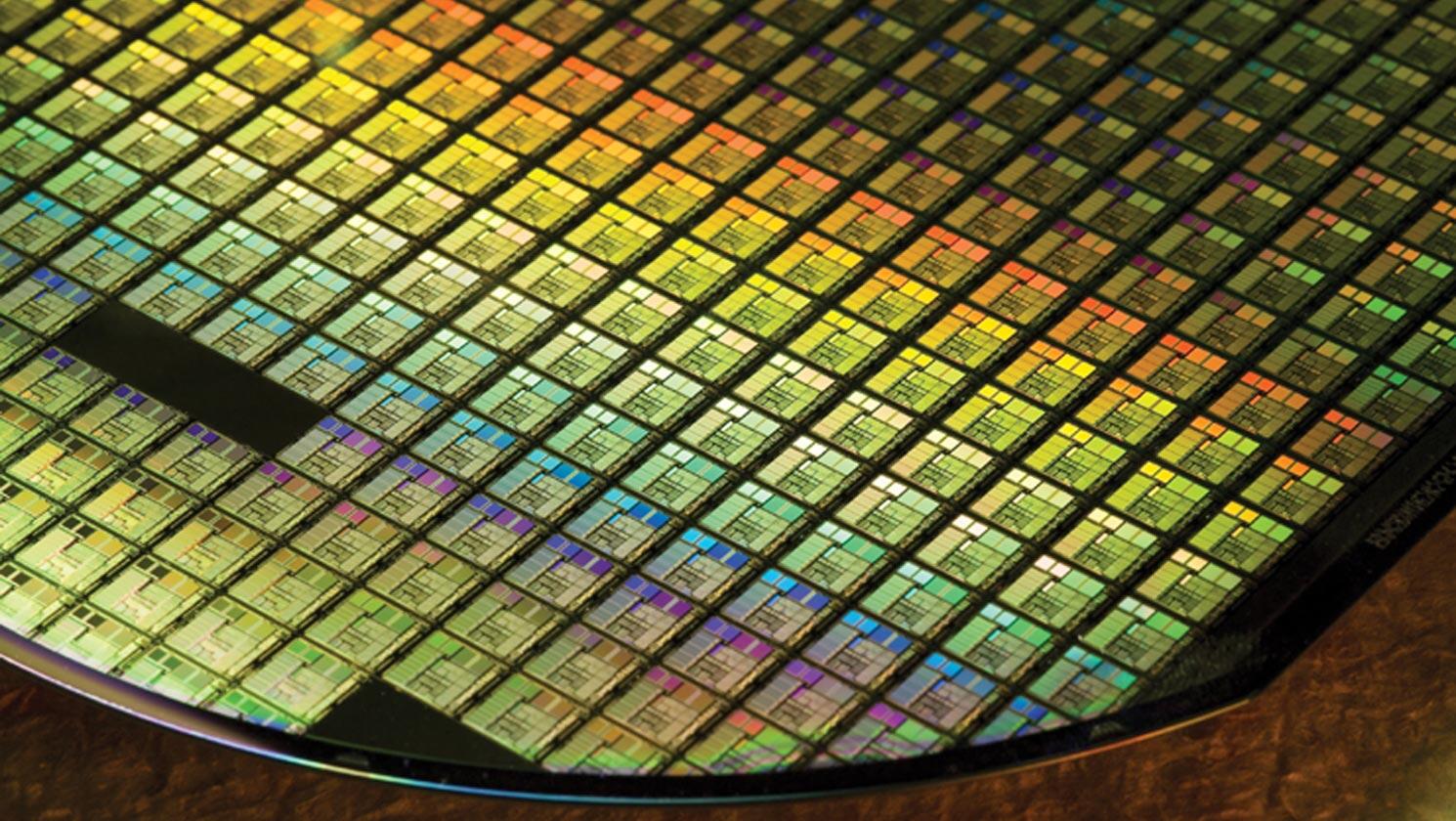

Il “tasso di rendimento” menzionato nel discorso si riferisce principalmente al numero di chip che superano determinati test in un “wafer”. Ci sono molti fattori chiave che influenzano il tasso di rendimento, tra cui i materiali, parametri e macchinari utilizzati. Tutto va esaminato nel dettaglio al fine di ottenere i migliori risultati possibili.

L’attuale tasso di resa da un wafer TSMC da 3 nm è di circa il 60-70%, ma TSMC promette di arrivare tra il 75 e l’80%. Se così fosse, sia Apple che Qualcomm non avrebbero alcun problema di disponibilità per i loro prossimi chip: A17 Bionic e Snapdragon 8 Gen 3. Allo stesso tempo, il tasso di rendimento dei wafer con chip a 3 nm di Samsung è solo del 20% e, in alcuni casi, si arriva al 10%, con molte differenze tra un wafer e l’altro. Per gli analisti questo tipo di risultato significa una sola cosa: non hanno ancora capito dov’è il problema. Se possiamo fidarci di questi dati, Apple e Qualcomm non avranno problemi di spedizione per i loro chipset di nuova generazione, l’A17 Bionic e lo Snapdragon 8 Gen 3.

Inoltre, un miglior tasso di resa indica anche un contenimento dei costi. Questo avviene perché il prezzo viene stabilito per singolo wafer. Quindi, se un singolo wafer ha un tasso di rendimento migliore, si potranno utilizzare più chip e, di conseguenza, acquistarne meno. Risultati peggiori, invece, costringerebbero le aziende ad acquistare più wafer, con conseguenti aumenti dei costi che, sul medio-lungo termine, non gioverebbero a nessuno.

Fonte: bnext